EH25 45

Series —

RoHS Compliant (Pb-free) 5.0V 4 Pad 5mm x 7mm

Ceramic SMD HCMOS/TTL High Frequency Oscillator

Frequency Tolerance/Stability ±50ppm Maximum

Operating Temperature Range - 0°C to +70°C

TS -24.576M

Nominal Frequency 24.576MHz

Pin 1 Connection

Tri-State (High Impedance)

Duty Cycle 50 ±10(%)

| #50ppm Maximum (Inclusive of all conditions: Calibration Tolerance at 25°C, Frequency Stability over the Operating Temperature Range, Supply Voltage Change, Output Load Change, First Year Aging at 25°C, Shock, and Vibration)  Aging at 25°C  #5ppm/year Maximum  Operating Temperature Range  O°C to +70°C  Supply Voltage  Input Current  SomA Maximum (No Load)  Output Voltage Logic High (Voh)  Output Voltage Logic Low (Vol)  All Voltage Logic Low (Vol)  Output Voltage Logic Low (Vol)  One Capability  Output Logic Type  CMOS  Pin 1 Connection  Tri-State Input Voltage (Vih and Vil)  Tri-State Input Voltage (Vih and Vil)  Absolute Clock Jitter  #250pSec Maximum, ±100pSec Typical  Start Up Time  #50ppm Maximum (Inclusive of all conditions: Calibration Tolerance at 25°C, Shock, and Vibration)  #50ppm Maximum (Inclusive of all conditions: Calibration Tolerance at 25°C, Shock, and Vibration)  #50ppm/year Maximum  #50ppm Maximum (Inclusive of all conditions: Calibration Change, Disput Voltage Change, Output Load Change, Pirst Year Aging at 25°C, Shock, and Vibration)  #50ppm Maximum (Notations)  #50ppm Maximum (Inclusive Range, Supply Voltage Change, Output Load Change, Pirst Year Aging at 25°C, Shock, and Vibration)  #50ppm Maximum (Notations)  #50ppm Maximum (Notations)  #50ppm Maximum (Inclusive Additions)  #50ppm Maximum (Notations)  #50ppm Maximum (Notatio | ELECTRICAL SPECIFICATIONS             |                                                                                                                    |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|

| Aging at 25°C Aging at 25°C Aging at 25°C Aging at 25°C  Aging at 25°C  Aging at 25°C  Derating Temperature Range  O°C to +70°C  Supply Voltage  Soma Maximum (No Load)  Output Voltage Logic High (Voh)  Output Voltage Logic Low (Vol)  Rise/Fall Time  One Sigma Clock Period Jitter  Aging at 25°C, Shock, and Vibration)  Aging at 25°C  Aging at 25°  Aging a | Nominal Frequency                     | 24.576MHz                                                                                                          |  |

| Operating Temperature Range 0°C to +70°C  Supply Voltage 5.0Vdc ±10%  Input Current 50mA Maximum (No Load)  Output Voltage Logic High (Voh) 2.4Vdc Minimum with TTL Load, Vdd-0.4Vdc Minimum with HCMOS Load (IOH= -16mA)  Output Voltage Logic Low (Vol) 0.4Vdc Maximum with TTL Load, 0.5Vdc Maximum with HCMOS Load (IOH= +16mA)  Rise/Fall Time 6.0Sec Maximum (Measured at 0.8Vdc to 2.0Vdc with TTL Load; Measured at 20% to 80% of waveform with HCMOS Load)  Duty Cycle 50 ±10(%) (Measured at 1.4Vdc with TTL Load; Measured at 50% of waveform with HCMOS Load)  Load Drive Capability 10TTL Load or 50pF HCMOS Load Maximum  Output Logic Type CMOS  Pin 1 Connection 7ri-State (High Impedance)  Tri-State Input Voltage (Vih and Vil) +2.2Vdc Minimum to enable output, +0.8Vdc Maximum to disable output (High Impedance), No Connect to enable output  Absolute Clock Jitter ±250pSec Maximum, ±100pSec Typical  Start Up Time 10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Frequency Tolerance/Stability         | Operating Temperature Range, Supply Voltage Change, Output Load Change, First Year Aging at 25°C,                  |  |

| Supply Voltage 5.0Vdc ±10%  Input Current 50mA Maximum (No Load)  Output Voltage Logic High (Voh) 2.4Vdc Minimum with TTL Load, Vdd-0.4Vdc Minimum with HCMOS Load (IOH= -16mA)  Output Voltage Logic Low (Vol) 0.4Vdc Maximum with TTL Load, 0.5Vdc Maximum with HCMOS Load (IOH= +16mA)  Rise/Fall Time 6nSec Maximum (Measured at 0.8Vdc to 2.0Vdc with TTL Load; Measured at 20% to 80% of waveform with HCMOS Load)  Duty Cycle 50 ±10(%) (Measured at 1.4Vdc with TTL Load; Measured at 50% of waveform with HCMOS Load)  Load Drive Capability 10TTL Load or 50pF HCMOS Load Maximum  Output Logic Type CMOS  Pin 1 Connection 7ri-State (High Impedance)  Tri-State Input Voltage (Vih and Vil) +2.2Vdc Minimum to enable output, +0.8Vdc Maximum to disable output (High Impedance), No Connect to enable output.  Absolute Clock Jitter ±250pSec Maximum, ±100pSec Typical  Start Up Time 10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Aging at 25°C                         | ±5ppm/year Maximum                                                                                                 |  |

| Input Current  50mA Maximum (No Load)  Output Voltage Logic High (Voh)  2.4Vdc Minimum with TTL Load, Vdd-0.4Vdc Minimum with HCMOS Load (IOH= -16mA)  Output Voltage Logic Low (Vol)  0.4Vdc Maximum with TTL Load, 0.5Vdc Maximum with HCMOS Load (IOH= +16mA)  Rise/Fall Time  6nSec Maximum (Measured at 0.8Vdc to 2.0Vdc with TTL Load; Measured at 20% to 80% of waveform with HCMOS Load)  Duty Cycle  50 ±10(%) (Measured at 1.4Vdc with TTL Load; Measured at 50% of waveform with HCMOS Load)  Load Drive Capability  10TTL Load or 50pF HCMOS Load Maximum  Output Logic Type  CMOS  Pin 1 Connection  Tri-State (High Impedance)  Tri-State Input Voltage (Vih and Vil)  +2.2Vdc Minimum to enable output, +0.8Vdc Maximum to disable output (High Impedance), No Connect to enable output.  Absolute Clock Jitter  ±250pSec Maximum, ±100pSec Typical  50mSec Maximum, ±30pSec Typical  10mSec Maximum  10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Operating Temperature Range           | 0°C to +70°C                                                                                                       |  |

| Output Voltage Logic High (Voh)  2.4Vdc Minimum with TTL Load, Vdd-0.4Vdc Minimum with HCMOS Load (IOH= -16mA)  0.4Vdc Maximum with TTL Load, 0.5Vdc Maximum with HCMOS Load (IOH= +16mA)  Rise/Fall Time  6nSec Maximum (Measured at 0.8Vdc to 2.0Vdc with TTL Load; Measured at 20% to 80% of waveform with HCMOS Load)  Duty Cycle  50 ±10(%) (Measured at 1.4Vdc with TTL Load; Measured at 50% of waveform with HCMOS Load)  Load Drive Capability  10TTL Load or 50pF HCMOS Load Maximum  Output Logic Type  CMOS  Pin 1 Connection  Tri-State (High Impedance)  Tri-State Input Voltage (Vih and Vil)  +2.2Vdc Minimum to enable output, +0.8Vdc Maximum to disable output (High Impedance), No Connect to enable output.  Absolute Clock Jitter  2.50pSec Maximum, ±100pSec Typical  50pSec Maximum, ±30pSec Typical  10mSec Maximum  10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Supply Voltage                        | 5.0Vdc ±10%                                                                                                        |  |

| Output Voltage Logic Low (Vol)  0.4Vdc Maximum with TTL Load, 0.5Vdc Maximum with HCMOS Load (IOH= +16mA)  6nSec Maximum (Measured at 0.8Vdc to 2.0Vdc with TTL Load; Measured at 20% to 80% of waveform with HCMOS Load)  Duty Cycle  50 ±10(%) (Measured at 1.4Vdc with TTL Load; Measured at 50% of waveform with HCMOS Load)  Load Drive Capability  10TTL Load or 50pF HCMOS Load Maximum  Output Logic Type  CMOS  Pin 1 Connection  Tri-State (High Impedance)  Tri-State Input Voltage (Vih and Vil)  +2.2Vdc Minimum to enable output, +0.8Vdc Maximum to disable output (High Impedance), No Connect to enable output.  Absolute Clock Jitter  ±250pSec Maximum, ±100pSec Typical  50pSec Maximum, ±30pSec Typical  10mSec Maximum  10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Input Current                         | 50mA Maximum (No Load)                                                                                             |  |

| Rise/Fall Time  6nSec Maximum (Measured at 0.8Vdc to 2.0Vdc with TTL Load; Measured at 20% to 80% of waveform with HCMOS Load)  Duty Cycle  50 ±10(%) (Measured at 1.4Vdc with TTL Load; Measured at 50% of waveform with HCMOS Load)  Load Drive Capability  10TTL Load or 50pF HCMOS Load Maximum  Output Logic Type  CMOS  Pin 1 Connection  Tri-State (High Impedance)  Tri-State Input Voltage (Vih and Vil)  +2.2Vdc Minimum to enable output, +0.8Vdc Maximum to disable output (High Impedance), No Connect to enable output.  Absolute Clock Jitter  ±250pSec Maximum, ±100pSec Typical  One Sigma Clock Period Jitter  10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Output Voltage Logic High (Voh)       | 2.4Vdc Minimum with TTL Load, Vdd-0.4Vdc Minimum with HCMOS Load (IOH= -16mA)                                      |  |

| with HCMOS Load)Duty Cycle50 ±10(%) (Measured at 1.4Vdc with TTL Load; Measured at 50% of waveform with HCMOS Load)Load Drive Capability10TTL Load or 50pF HCMOS Load MaximumOutput Logic TypeCMOSPin 1 ConnectionTri-State (High Impedance)Tri-State Input Voltage (Vih and Vil)+2.2Vdc Minimum to enable output, +0.8Vdc Maximum to disable output (High Impedance), No Connect to enable output.Absolute Clock Jitter±250pSec Maximum, ±100pSec TypicalOne Sigma Clock Period Jitter±50pSec Maximum, ±30pSec TypicalStart Up Time10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Output Voltage Logic Low (Vol)        | 0.4Vdc Maximum with TTL Load, 0.5Vdc Maximum with HCMOS Load (IOH= +16mA)                                          |  |

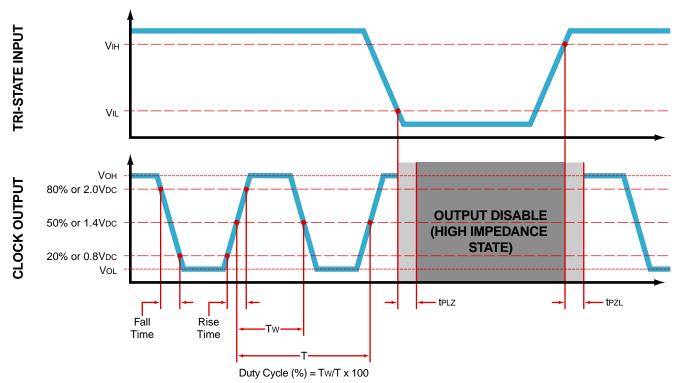

| Load Drive Capability     10TTL Load or 50pF HCMOS Load Maximum       Output Logic Type     CMOS       Pin 1 Connection     Tri-State (High Impedance)       Tri-State Input Voltage (Vih and Vil)     +2.2Vdc Minimum to enable output, +0.8Vdc Maximum to disable output (High Impedance), No Connect to enable output.       Absolute Clock Jitter     ±250pSec Maximum, ±100pSec Typical       One Sigma Clock Period Jitter     ±50pSec Maximum, ±30pSec Typical       Start Up Time     10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Rise/Fall Time                        |                                                                                                                    |  |

| Output Logic Type  CMOS  Pin 1 Connection  Tri-State (High Impedance)  +2.2Vdc Minimum to enable output, +0.8Vdc Maximum to disable output (High Impedance), No Connect to enable output.  Absolute Clock Jitter  ±250pSec Maximum, ±100pSec Typical  One Sigma Clock Period Jitter  ±50pSec Maximum, ±30pSec Typical  Start Up Time  10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Duty Cycle                            | 50 ±10(%) (Measured at 1.4Vdc with TTL Load; Measured at 50% of waveform with HCMOS Load)                          |  |

| Pin 1 Connection  Tri-State (High Impedance)  Tri-State Input Voltage (Vih and Vil)  +2.2Vdc Minimum to enable output, +0.8Vdc Maximum to disable output (High Impedance), No Connect to enable output.  Absolute Clock Jitter  ±250pSec Maximum, ±100pSec Typical  One Sigma Clock Period Jitter  ±50pSec Maximum, ±30pSec Typical  10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Load Drive Capability                 | 10TTL Load or 50pF HCMOS Load Maximum                                                                              |  |

| Tri-State Input Voltage (Vih and Vil) +2.2Vdc Minimum to enable output, +0.8Vdc Maximum to disable output (High Impedance), No Connect to enable Clock Jitter  +2.50pSec Maximum, ±100pSec Typical  One Sigma Clock Period Jitter  ±50pSec Maximum, ±30pSec Typical  Start Up Time  10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Output Logic Type                     | CMOS                                                                                                               |  |

| enable output.  Absolute Clock Jitter ±250pSec Maximum, ±100pSec Typical  One Sigma Clock Period Jitter ±50pSec Maximum, ±30pSec Typical  Start Up Time 10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pin 1 Connection                      | Tri-State (High Impedance)                                                                                         |  |

| One Sigma Clock Period Jitter ±50pSec Maximum, ±30pSec Typical  Start Up Time 10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Tri-State Input Voltage (Vih and Vil) | +2.2Vdc Minimum to enable output, +0.8Vdc Maximum to disable output (High Impedance), No Connect to enable output. |  |

| Start Up Time 10mSec Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Absolute Clock Jitter                 | ±250pSec Maximum, ±100pSec Typical                                                                                 |  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | One Sigma Clock Period Jitter         | ±50pSec Maximum, ±30pSec Typical                                                                                   |  |

| Storage Temperature Range -55°C to +125°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Start Up Time                         | 10mSec Maximum                                                                                                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Storage Temperature Range             | -55°C to +125°C                                                                                                    |  |

| ENVIRONMENTAL & MECHANICAL SPECIFICATIONS |                                               |  |

|-------------------------------------------|-----------------------------------------------|--|

| ESD Susceptibility                        | MIL-STD-883, Method 3015, Class 1, HBM: 1500V |  |

| Fine Leak Test                            | MIL-STD-883, Method 1014, Condition A         |  |

| Flammability                              | UL94-V0                                       |  |

| Gross Leak Test                           | MIL-STD-883, Method 1014, Condition C         |  |

| Mechanical Shock                          | MIL-STD-883, Method 2002, Condition B         |  |

| Moisture Resistance                       | MIL-STD-883, Method 1004                      |  |

| Moisture Sensitivity                      | J-STD-020, MSL 1                              |  |

| Resistance to Soldering Heat              | MIL-STD-202, Method 210, Condition K          |  |

| Resistance to Solvents                    | MIL-STD-202, Method 215                       |  |

| Solderability                             | MIL-STD-883, Method 2003                      |  |

| Temperature Cycling                       | MIL-STD-883, Method 1010, Condition B         |  |

| Vibration                                 | MIL-STD-883, Method 2007, Condition A         |  |

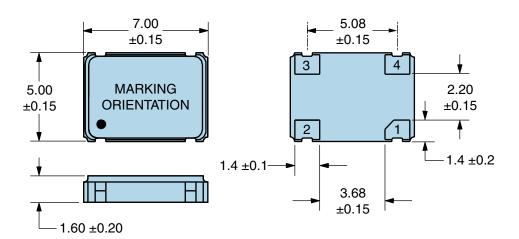

### **MECHANICAL DIMENSIONS (all dimensions in millimeters)**

| PIN | CONNECTION     |

|-----|----------------|

| 1   | Tri-State      |

| 2   | Ground         |

| 3   | Output         |

| 4   | Supply Voltage |

| LINE | MARKING                                              |

|------|------------------------------------------------------|

| 1    | ECLIPTEK                                             |

| 2    | 24.576M                                              |

| 3    | XXXXXX<br>XXXXX=Ecliptek<br>Manufacturing Identifier |

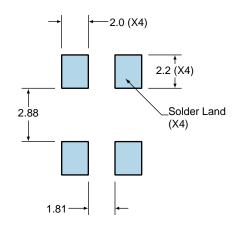

#### **Suggested Solder Pad Layout**

All Dimensions in Millimeters

All Tolerances are ±0.1

#### **OUTPUT WAVEFORM & TIMING DIAGRAM**

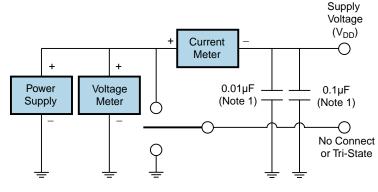

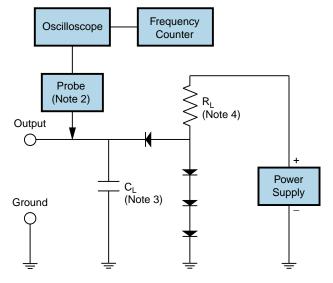

#### **Test Circuit for TTL Output**

| Output Load<br>Drive Capability | R <sub>L</sub> Value<br>(Ohms) | C <sub>L</sub> Value<br>(pF) |

|---------------------------------|--------------------------------|------------------------------|

| 10TTL                           | 390                            | 15                           |

| 5TTL                            | 780                            | 15                           |

| 2TTL                            | 1100                           | 6                            |

| 10LSTTL                         | 2000                           | 15                           |

| 1TTL                            | 2200                           | 3                            |

Table 1:  $R_L$  Resistance Value and  $C_L$  Capacitance Value Vs. Output Load Drive Capability

Note 1: An external  $0.1\mu F$  low frequency tantalum bypass capacitor in parallel with a  $0.01\mu F$  high frequency ceramic bypass capacitor close to the package ground and  $V_{DD}$  pin is required.

Note 2: A low capacitance (<12pF), 10X attenuation factor, high impedance (>10Mohms), and high bandwidth (>300MHz) passive probe is recommended.

Note 3: Capacitance value  $C_{\mathsf{L}}$  includes sum of all probe and fixture capacitance.

Note 4: Resistance value R<sub>L</sub> is shown in Table 1. See applicable specification sheet for 'Load Drive Capability'.

Note 5: All diodes are MMBD7000, MMBD914, or equivalent.

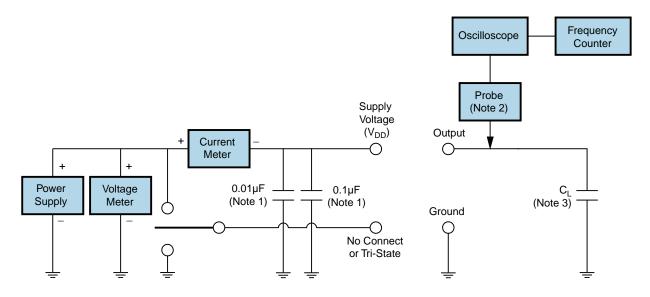

### **Test Circuit for CMOS Output**

Note 1: An external  $0.1\mu\text{F}$  low frequency tantalum bypass capacitor in parallel with a  $0.01\mu\text{F}$  high frequency ceramic bypass capacitor close to the package ground and  $V_{DD}$  pin is required.

Note 2: A low capacitance (<12pF), 10X attenuation factor, high impedance (>10Mohms), and high bandwidth (>300MHz) passive probe is recommended.

Note 3: Capacitance value  $\dot{C}_L$  includes sum of all probe and fixture capacitance.

## **Recommended Solder Reflow Methods**

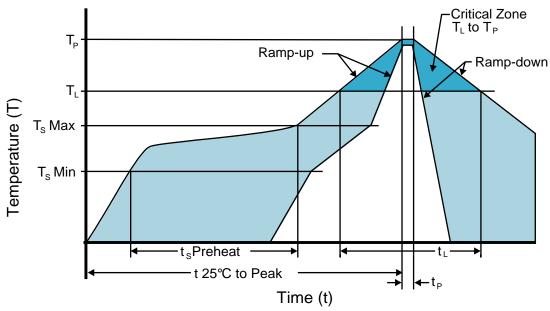

### **High Temperature Infrared/Convection**

| <u> </u>                                            |                                                   |

|-----------------------------------------------------|---------------------------------------------------|

| T <sub>s</sub> MAX to T <sub>∟</sub> (Ramp-up Rate) | 3°C/second Maximum                                |

| Preheat                                             |                                                   |

| - Temperature Minimum (T <sub>S</sub> MIN)          | 150°C                                             |

| - Temperature Typical (T <sub>s</sub> TYP)          | 175°C                                             |

| - Temperature Maximum (T <sub>s</sub> MAX)          | 200°C                                             |

| - Time (t <sub>s</sub> MIN)                         | 60 - 180 Seconds                                  |

| Ramp-up Rate (T <sub>L</sub> to T <sub>P</sub> )    | 3°C/second Maximum                                |

| Time Maintained Above:                              |                                                   |

| - Temperature (T∟)                                  | 217°C                                             |

| - Time (t∟)                                         | 60 - 150 Seconds                                  |

| Peak Temperature (T <sub>P</sub> )                  | 260°C Maximum for 10 Seconds Maximum              |

| Target Peak Temperature (T <sub>P</sub> Target)     | 250°C +0/-5°C                                     |

| Time within 5°C of actual peak (tp)                 | 20 - 40 seconds                                   |

| Ramp-down Rate                                      | 6°C/second Maximum                                |

| Time 25°C to Peak Temperature (t)                   | 8 minutes Maximum                                 |

| Moisture Sensitivity Level                          | Level 1                                           |

| Additional Notes                                    | Temperatures shown are applied to body of device. |

|                                                     |                                                   |

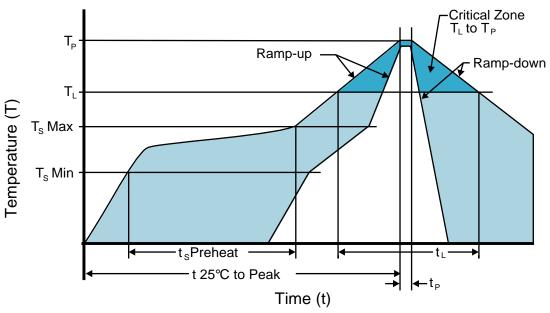

### **Recommended Solder Reflow Methods**

### Low Temperature Infrared/Convection 240°C

| T <sub>S</sub> MAX to T <sub>L</sub> (Ramp-up Rate) | 5°C/second Maximum                                     |

|-----------------------------------------------------|--------------------------------------------------------|

| Preheat                                             |                                                        |

| - Temperature Minimum (T <sub>s</sub> MIN)          | N/A                                                    |

| - Temperature Typical (T <sub>S</sub> TYP)          | 150°C                                                  |

| - Temperature Maximum (T <sub>s</sub> MAX)          | N/A                                                    |

| - Time (t <sub>s</sub> MIN)                         | 60 - 120 Seconds                                       |

| Ramp-up Rate (T <sub>L</sub> to T <sub>P</sub> )    | 5°C/second Maximum                                     |

| Time Maintained Above:                              |                                                        |

| - Temperature (T∟)                                  | 150°C                                                  |

| - Time (t∟)                                         | 200 Seconds Maximum                                    |

| Peak Temperature (T <sub>P</sub> )                  | 240°C Maximum                                          |

| Target Peak Temperature (T <sub>P</sub> Target)     | 240°C Maximum 1 Time / 230°C Maximum 2 Times           |

| Time within 5°C of actual peak (tp)                 | 10 seconds Maximum 2 Times / 80 seconds Maximum 1 Time |

| Ramp-down Rate                                      | 5°C/second Maximum                                     |

| Time 25°C to Peak Temperature (t)                   | N/A                                                    |

| Moisture Sensitivity Level                          | Level 1                                                |

| Additional Notes                                    | Temperatures shown are applied to body of device.      |

### **Low Temperature Manual Soldering**

185°C Maximum for 10 seconds Maximum, 2 times Maximum. (Temperatures shown are applied to body of device.)

### **High Temperature Manual Soldering**

260°C Maximum for 5 seconds Maximum, 2 times Maximum. (Temperatures shown are applied to body of device.)